- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC32MX250F128B-I/SP (Microchip Technology)IC MCU 32BIT 128KB FLASH 28-SDIP

PIC32MX1XX/2XX

DS61168D-page 100

Preliminary

2011-2012 Microchip Technology Inc.

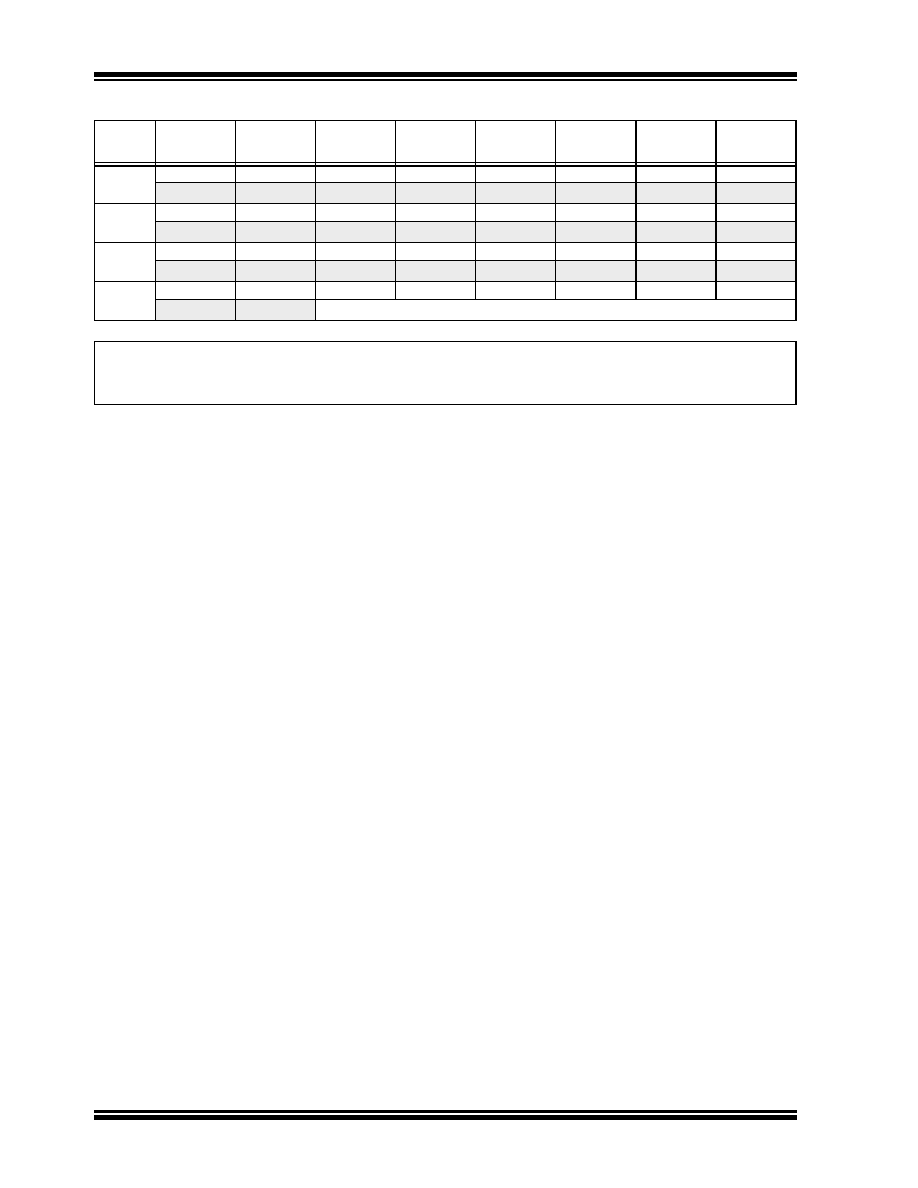

REGISTER 8-2:

OSCTUN: FRC TUNING REGISTER(1)

Bit

Range

Bit

31/23/15/7

Bit

30/22/14/6

Bit

29/21/13/5

Bit

28/20/12/4

Bit

27/19/11/3

Bit

26/18/10/2

Bit

25/17/9/1

Bit

24/16/8/0

31:24

U-0

—

23:16

U-0

R-0

U-0

—

15:8

U-0

R-0

U-0

—

7:0

U-0

R/W-0

—

TUN<5:0>(2)

Legend:

y = Value set from Configuration bits on POR

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 31-6

Unimplemented: Read as ‘0’

bit 5-0

TUN<5:0>: FRC Oscillator Tuning bits(2)

100000 = Center frequency -12.5%

100001 =

111111 =

000000 = Center frequency. Oscillator runs at minimal frequency (8 MHz)

000001 =

011110 =

011111 = Center frequency +12.5%

Note 1: Writes to this register require an unlock sequence. Refer to Section 6. “Oscillator” (DS61112) in the

“PIC32 Family Reference Manual” for details.

2: OSCTUN functionality has been provided to help customers compensate for temperature effects on the

FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither

characterized, nor tested.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F47J53-I/PT

IC PIC MCU 128KB FLASH 44TQFP

DSPIC30F1010-30I/SP

IC DSPIC MCU/DSP 6K 28DIP

PIC24FJ64GB002-I/ML

IC MCU 16BIT 64KB FLASH 28QFN

52746-1270

CONN FFC 12POS .5MM R/A ZIF SMD

TS80C31X2-MCE

IC MCU 8BIT 40/20MHZ 44-VQFP

52746-0870

CONN FFC 8POS .5MM R/A ZIF SMD

PIC24FJ128GA008-I/PT

IC PIC MCU FLASH 128K 80TQFP

PIC16F737-I/SP

IC PIC MCU FLASH 4KX14 28DIP

相关代理商/技术参数

PIC32MX250F128B-I/SP

制造商:Microchip Technology Inc 功能描述:32 Bit MCU 128KB Flash 32KB RAM 40 MH 制造商:Microchip Technology Inc 功能描述:IC, 32BIT MCU, PIC32, 40MHz, DIP-28

PIC32MX250F128B-I/SS

功能描述:32位微控制器 - MCU 32B 128KB FL 32KB RAM 40MHz 28 Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX250F128BT-50I/ML

制造商:Microchip Technology Inc 功能描述:32-BIT FAMILY, 128KB FLASH, 32 KB RAM, 50MHZ - Tape and Reel 制造商:Microchip Technology Inc 功能描述:IC MCU 32BIT 128KB FLASH 28QFN 制造商:Microchip Technology Inc 功能描述:32-bit family, 128KB FLASH, 32 KB RAM, 50MHz, 28 QFN 6x6x0.9mm T/R

PIC32MX250F128BT-50I/SO

制造商:Microchip Technology Inc 功能描述:32-BIT FAMILY, 128KB FLASH, 32 KB RAM, 50MHZ - Tape and Reel 制造商:Microchip Technology Inc 功能描述:IC MCU 32BIT 128KB FLASH 28SOIC 制造商:Microchip Technology Inc 功能描述:32-bit family, 128KB FLASH, 32 KB RAM, 50MHz, 28 SOIC .300in T/R

PIC32MX250F128BT-50I/SS

制造商:Microchip Technology Inc 功能描述:32-BIT FAMILY, 128KB FLASH, 32 KB RAM, 50MHZ - Tape and Reel 制造商:Microchip Technology Inc 功能描述:IC MCU 32BIT 128KB FLASH 28SSOP 制造商:Microchip Technology Inc 功能描述:32-bit family, 128KB FLASH, 32 KB RAM, 50MHz, 28 SSOP .209in T/R

PIC32MX250F128BT-I/ML

功能描述:32位微控制器 - MCU 32B 128KB FL 32KB RAM 40MHz 28 Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX250F128BT-I/SO

功能描述:32位微控制器 - MCU 32B 128KB FL 32KB RAM 40MHz 28 Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX250F128BT-I/SS

功能描述:32位微控制器 - MCU 32B 128KB FL 32KB RAM 40MHz 28 Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT